AI Training Data Copyright Crisis: Lawsuits & Solutions

TL;DR: TPUs and GPUs represent divergent AI acceleration philosophies: Google's TPUs excel at large-batch inference with 2× better performance-per-watt and superior cost-efficiency for stable workloads, while NVIDIA's GPUs dominate through CUDA ecosystem maturity, architectural flexibility, and multi-cloud availability. The choice hinges on framework (TensorFlow/JAX favors TPUs, PyTorch favors GPUs), cloud strategy (GCP-only vs multi-cloud), and workload (predictable batch processing vs mixed/exploratory tasks). As AMD, Intel, and startups enter the fray, the future points toward heterogeneous infrastructure routing workloads to specialized accelerators—but the civilization-scale question remains: will AI compute concentrate in a few hyperscalers' hands, or democratize across nations and communities?

By 2030, the choice between Tensor Processing Units and Graphics Processing Units will determine which nations lead the AI revolution—and which fall behind. While Silicon Valley bets billions on NVIDIA's GPU empire, Google's TPU infrastructure quietly powers the algorithms that shape three billion daily searches, YouTube recommendations, and breakthrough protein folding that won a Nobel Prize. This isn't just a technical debate about chips—it's a strategic decision that will define economic competitiveness, energy sustainability, and technological sovereignty for decades to come.

At their core, TPUs and GPUs represent fundamentally different philosophies about how to accelerate artificial intelligence. TPUs are Application-Specific Integrated Circuits (ASICs) purpose-built for one thing: tensor operations. Google designed them from silicon up to execute the matrix multiplications that power neural networks, using a systolic array architecture where data flows through a grid of processing elements in perfect synchronization. Each TPU chip houses dedicated Matrix Multiply Units (MXUs) that perform thousands of multiply-accumulate operations simultaneously, with high-bandwidth memory (HBM) feeding data at speeds up to 7.37 TB/s in the latest Ironwood generation.

GPUs, by contrast, evolved from graphics rendering into general-purpose parallel processors. NVIDIA's chips contain thousands of CUDA cores—specialized compute units that can execute diverse workloads beyond just AI. The H100 GPU packs 16,896 CUDA cores alongside tensor cores optimized for mixed-precision math, delivering up to 1,979 teraflops for FP16 calculations. This architectural flexibility comes with trade-offs: GPUs rely on complex memory hierarchies with L1 cache, L2 cache (split into 32 MB partitions on the A100), and external GDDR or HBM memory, creating potential bottlenecks when data must traverse between cores.

The systolic array design in TPUs eliminates the Von Neumann bottleneck that plagues traditional computing. Instead of fetching data from memory for every operation, TPUs load parameters once into the array and stream data through, with results passing directly between processing elements. This "data locality" approach means a TPU processing element consumes just 2.17 milliwatts for a 32-bit floating-point multiply-accumulate operation—far less than GPU cores that must shuttle data across longer distances. The architectural choice reflects a core insight: for the massive batch processing that dominates AI training and inference, predictable data flow beats flexible programmability.

Raw computational throughput tells only part of the story. Google's TPU v5p delivers 918 int8 TFLOP/s at 170W, achieving approximately 5.4 TFLOP/s per watt. NVIDIA's H100 counters with up to 2,000 teraflops in specialized modes but consumes up to 700W at peak load. On paper, the H100's absolute performance dwarfs earlier TPU generations—but the real-world comparison depends entirely on workload characteristics.

MLPerf benchmarks reveal where each architecture dominates. For GPT-3 training, a system of 11,616 H100 GPUs completed the benchmark in 3.44 minutes, crushing a 6,144-chip TPU v5p cluster that required 11.77 minutes. The GPU advantage stems from NVIDIA's massive investment in tensor cores, transformer engines, and low-latency NVLink interconnects that move data between chips at 900 GB/s per connection. Yet for inference workloads—where models respond to user queries rather than training on vast datasets—TPUs reverse the equation. Inception-v3 image recognition runs 3.1× faster on TPU v4-8 pods compared to A100 GPUs at batch size 8, thanks to TPUs' optimized pipeline for streaming predictions through the systolic array.

Batch size emerges as the critical variable. Increasing batch size from 1 to 64 on an H100 boosts throughput by 39× for LLaMA-3-70B, while the same increase on an A100 yields only a 3× improvement. This scaling behavior reflects GPU memory bandwidth evolution: the H100's HBM3 memory delivers 3.35 TB/s compared to HBM2e in the A100. TPUs, however, maintain more consistent performance across batch sizes because their systolic architecture inherently processes large batches—the v5p's 1,640 GB/s memory bandwidth per chip feeds a design optimized for throughput over latency.

The newest entrants push boundaries further. Google's Ironwood TPU, announced in 2025, reaches 4,614 TFLOP/s per chip with 192 GB of HBM and 7.37 TB/s bandwidth—6× the memory capacity of its predecessor, Trillium. At full pod scale (9,216 chips), Ironwood delivers 42.5 exaflops, surpassing the world's largest supercomputer, El Capitan, by 24×. NVIDIA's roadmap counters with the Blackwell B200, which roughly doubles H100 performance per GPU for transformer workloads, leveraging 4-bit precision for key operations and projected 20 petaflops per core.

When OpenAI began leasing Google Cloud TPUs in 2024 to diversify away from exclusive reliance on Microsoft-managed NVIDIA infrastructure, the decision signaled a fundamental shift: inference cost matters as much as training speed. Running a one-hour GPT-4.5 conversation on dedicated H100 hardware costs approximately $40–70 in a straightforward cloud setup, accounting for GPU rental ($12.30/hour per chip), electricity (5.6 kWh at $0.12/kWh), cooling, and maintenance. Google claims its TPU-based inference systems deliver 2–4× better performance per dollar than GPU setups, making them economically superior for high-volume, sustained workloads like search ranking and recommendation engines.

Cloud pricing reflects these trade-offs. Google Cloud's TPU v5p costs roughly $3.50/hour for training pods, compared to $4.50–6.00/hour for NVIDIA H100 instances on major clouds. AWS charges $55.04/hour for an 8×H100 instance in us-east-1, while Azure's equivalent runs $98.32/hour. Yet neo-cloud providers like DataCrunch undercut hyperscalers dramatically: H100 instances start at $1.99/hour, and dynamic pricing can reduce costs by 40% during off-peak periods. A TPU v4-pod (4,096 chips) costs $32,200/hour on-demand—a staggering figure until you compare performance-per-dollar for specific tasks. For Escalante's protein design workloads, spot TPU v6e (Trillium) achieved 3.65× better cost efficiency than equivalent H100 runs, translating massive training jobs from days to hours at a fraction of the expense.

Energy efficiency increasingly drives architecture decisions as data centers confront power constraints. TPU v4 achieves 1.62 TOPS/watt, while Trillium improves energy efficiency by 67% over its predecessor—nearly 30× better than Google's first Cloud TPU from 2018. Ironwood doubles performance-per-watt again, reaching approximately 2× Trillium's efficiency. This relentless focus on power stems from a hard reality: training a large language model on thousands of GPUs for months can consume megawatt-hours of electricity, translating to millions in energy costs and substantial carbon emissions. A Dell Technologies system fine-tuned LLaMA 2 70B using just 75 cents of electricity in a 5-minute run, but scaling that to production workloads reveals the stakes. NVIDIA's GB200 Grace Blackwell Superchip demonstrates 25× energy efficiency over the prior Hopper generation for inference, yet the projected VR300 NVL576 rack will still consume over 600 kW—enough to power 400 homes.

The carbon accounting matters beyond cost. Financial services firm Murex achieved a 4× reduction in energy consumption and 7× faster completion when switching risk calculations from CPU-only systems to NVIDIA Grace Hopper Superchips. Accelerated computing systems using GPUs can save over 40 terawatt-hours annually across HPC and AI workloads compared to CPU-only alternatives—equivalent to the electricity consumption of Portugal. Yet the question remains: can specialized ASICs like TPUs push efficiency further? Google's sustainability mandate suggests yes, with each TPU generation designed to double performance while holding power constant or reducing it, whereas GPU power budgets keep climbing (H100 at 700W, projected Blackwell variants even higher).

Architectural superiority means nothing if developers can't write code for your chip. NVIDIA's CUDA platform, launched in 2006, gave researchers a C-style programming model that democratized GPU computing just as AlexNet proved neural networks could beat traditional computer vision. Nearly two decades later, CUDA remains the backbone of virtually 100% of deep learning infrastructure. The ecosystem extends far beyond a compiler: cuDNN accelerates neural network primitives, TensorRT optimizes inference, NCCL handles multi-GPU communication, and NVIDIA's NGC container catalog provides pre-tuned Docker images for every major framework. This "software-by-hardware design" philosophy creates immense lock-in—leaving CUDA feels almost impossible once you've optimized kernels, tuned memory hierarchies, and integrated tensor core operations.

TPUs counter with a different strategy: deep integration with Google's software stack. TensorFlow was designed alongside TPUs, with XLA (Accelerated Linear Algebra) compiler support baked in from the start. JAX, Google's NumPy-like framework for high-performance research, compiles directly to TPU via XLA, enabling functional programming patterns that map beautifully to systolic arrays. The Pallas kernel language offers low-level control for structured sparsity and custom data pipelines, particularly valuable for Mixture-of-Experts models and transformer variants. Yet PyTorch—the dominant framework in AI research—requires third-party bridges to run on TPUs, and many researchers report a steeper learning curve compared to CUDA's mature tooling.

This ecosystem asymmetry creates a fundamental choice: broad compatibility versus optimized performance. GPUs support TensorFlow, PyTorch, JAX, and custom CUDA kernels across multiple clouds (AWS, Azure, GCP, OCI) and on-premises hardware. TPUs work beautifully with TensorFlow and JAX on Google Cloud, but you can't buy TPU chips for your own data center, and multi-cloud deployments are impossible. For organizations requiring vendor flexibility or hybrid infrastructure, this constraint alone eliminates TPUs from consideration. For teams fully committed to Google Cloud and TensorFlow/JAX workflows, TPUs' price-performance advantages become compelling.

The human cost matters too. CUDA's complexity demands expertise in PTX assembly, driver management, and low-level kernel optimization to extract maximum performance. Many engineers spend days tuning thread configurations, memory alignment, and warp divergence—time that doesn't directly advance model quality. PyTorch's torch.compile and JAX's automatic kernel fusion aim to abstract this complexity, potentially narrowing the performance gap between manually optimized CUDA and high-level frameworks. Yet when milliseconds of latency determine user experience—as in high-frequency trading, autonomous vehicles, or real-time translation—the ability to drop down to hand-written CUDA kernels remains invaluable.

Google Search processes billions of queries daily on TPUs, leveraging RoBERTa and T5 models to understand intent and rank results. Training RoBERTa on TPU v4-128 pods completes in 3-4 days versus 7-10 days on 8-server DGX-A100 GPU clusters—a 1.9× speedup that translates to faster iteration and lower cost for models retrained frequently. Google Photos' image recognition, YouTube's recommendation engine, and the Nobel Prize-winning AlphaFold protein folding system all run on TPU infrastructure, demonstrating viability at planetary scale. The common thread: large-batch, predictable workloads where tensor operations dominate and model architectures remain stable long enough to justify TPU deployment.

OpenAI and Meta, by contrast, trained GPT-3 and LLaMA on massive GPU clusters, exploiting NVIDIA's ecosystem maturity and the flexibility to experiment with novel architectures. Autonomous driving systems from Tesla, Waymo, and Cruise rely on GPUs for sensor fusion, real-time object detection, and path planning—workloads that mix neural network inference with classical computer vision and require low-latency responses. Financial institutions use GPUs for risk modeling, fraud detection, and algorithmic trading, where mixed workloads (data preprocessing, model inference, statistical analysis) benefit from general-purpose compute. Healthcare imaging, drug discovery, and scientific simulation similarly favor GPUs' versatility.

The emergence of Mixture-of-Experts (MoE) models complicates the picture. These architectures activate only a subset of parameters per input, demanding high-bandwidth interconnects to route data between expert modules. Google's Ironwood TPU features 1.2 TBps bidirectional inter-chip interconnect (ICI), 1.5× faster than Trillium, specifically designed for MoE scaling. NVIDIA counters with NVLink 5, delivering 1.8 TB/s per port and enabling tightly coupled GPU clusters. Early benchmarks suggest TPUs hold an edge for inference-heavy MoE workloads, while GPUs maintain advantages in mixed training-inference pipelines where model architectures evolve rapidly.

Edge deployment reveals another dimension. NVIDIA's Jetson platform and Intel's Data Center GPU Max Series bring GPU acceleration to edge servers, robots, and embedded systems, leveraging the same CUDA ecosystem that powers cloud training. Google's Edge TPU—a compact ASIC delivering 4 trillion operations per second at 2W—enables on-device inference in Pixel phones, Nest cameras, and Coral development boards. This 2,000 GFLOP/s per watt efficiency makes battery-powered AI feasible, but limits use cases to models specifically compiled for the Edge TPU architecture.

NVIDIA's market dominance—estimated at 75% of AI accelerator revenue by 2028, per Citi Research—creates strategic vulnerabilities. U.S. export controls restrict H100 and A100 sales to China, prompting Beijing to accelerate domestic alternatives from Huawei (Ascend processors) and startups like Biren Technology. Yet replicating CUDA's two-decade software moat proves far harder than fabricating silicon. Meanwhile, TSMC manufactures both NVIDIA GPUs and Google TPUs in Taiwan, creating a single-point-of-failure for Western AI infrastructure that U.S. and European policymakers increasingly view as unacceptable.

Google's TPU exclusivity to Google Cloud Platform limits proliferation—you can't accidentally transfer TPU workloads to a foreign adversary's infrastructure, because TPUs only exist in Google's data centers. This vertical integration appeals to governments concerned about technology transfer but frustrates enterprises seeking multi-cloud resilience. The U.S. CHIPS Act and Europe's Chips Act funnel billions toward domestic semiconductor manufacturing, aiming to reshore advanced packaging and HBM production that currently concentrates in Asia. How these investments reshape TPU and GPU supply chains will profoundly impact availability and pricing through 2030.

Broadcom's dominance in SerDes (serializer-deserializer) technology that connects AI chips within servers and across racks introduces another chokepoint. Both Google and NVIDIA rely on Broadcom for high-speed interconnect IP, making innovations like Ironwood's 1.2 TBps ICI and NVLink 5's 1.8 TB/s per port dependent on a single vendor's roadmap. As AI scales from thousands to millions of interconnected accelerators, networking becomes as critical as compute—an insight driving hyperscalers toward custom silicon for switches and routers alongside their training chips.

AMD's Instinct MI350 series, unveiled in late 2024, promises to disrupt the duopoly. Using 3D hybrid bonding to stack eight chiplets per GPU, the MI350X achieves 288 GB of HBM3E memory per device and 2× throughput improvement per compute unit for BF16 operations compared to MI300. Infinity Fabric interconnects scale to 5.5 TB/s internal bandwidth and 153.6 GB/s bisectional bandwidth in 8-GPU configurations, targeting the same large-scale training workloads NVIDIA and Google chase. At $1.99–3.99/hour on cloud platforms—roughly half the cost of equivalent H100 capacity—AMD positions itself as the value alternative for budget-conscious AI teams.

Intel's re-entry with Gaudi accelerators and the Data Center GPU Max Series adds another competitor, leveraging oneAPI for cross-architecture portability. Yet ecosystem effects favor incumbents: PyTorch code migrates from CUDA to Intel's XPU backend with minimal changes (swapping cuda device references for xpu), but optimization remains immature compared to CUDA's finely tuned libraries. Startups like Groq (with its Language Processing Unit claiming 10× speed and 1/10th cost versus GPUs) and Cerebras (with wafer-scale integration) demonstrate that architectural innovation continues, but market penetration requires years of software ecosystem development that most cannot sustain.

The tantalizing question: will GPUs and ASICs converge or diverge? NVIDIA's tensor cores represent ASIC-like specialization embedded within general-purpose GPUs, capturing 80% of TPU efficiency while retaining CUDA programmability. Google's TPUs, conversely, add more general-purpose capability with each generation—Trillium's 3rd-generation SparseCore and host-DRAM offloading enable diverse workloads beyond pure dense matrix multiplication. If this convergence continues, the distinction may blur into a continuum of specialization, with developers choosing accelerators based on workflow maturity rather than fundamental architectural camps.

For AI engineers and organizations, the TPU-versus-GPU decision hinges on five critical factors:

1. Framework Lock-In: If your team builds in PyTorch and requires rapid experimentation with novel architectures, GPUs offer unmatched flexibility. If you've standardized on TensorFlow/JAX for production ML pipelines, TPUs deliver superior cost-performance.

2. Cloud Strategy: Multi-cloud or hybrid deployments mandate GPUs, available across AWS, Azure, GCP, OCI, and on-premises. Google Cloud exclusivity makes TPUs viable only for GCP-committed organizations.

3. Workload Characteristics: Large-batch training and inference on stable model architectures favor TPUs' systolic efficiency. Mixed workloads, low-latency requirements, or frequently changing models favor GPU versatility.

4. Scale and Budget: At massive scale (thousands of chips), TPUs' performance-per-dollar and performance-per-watt advantages compound dramatically. For smaller deployments or sporadic workloads, GPUs' lower upfront cost and pay-per-use flexibility win.

5. Talent and Expertise: CUDA engineers command high salaries, but the global talent pool dwarfs TPU specialists. Training costs and hiring challenges may outweigh raw silicon performance differences.

The broader insight transcends individual chip choices: AI infrastructure is fragmenting into specialized tiers. Edge inference uses ultra-efficient ASICs (Edge TPU, NVIDIA Orin). Large-batch cloud inference gravitates toward TPUs and inference-optimized GPUs (L4, H200). Exploratory research and mixed workloads remain GPU territory. Training the largest models demands purpose-built supercomputers—whether TPU pods or DGX SuperPods—optimized for multi-month runs. Organizations navigating this landscape will increasingly deploy heterogeneous fleets, routing workloads to the most economical hardware rather than standardizing on a single architecture.

Three decades ago, Microsoft's Windows monopoly determined which applications billions used daily. Two decades ago, Google's search algorithm shaped what information humanity accessed. Today, the hardware layer beneath AI models represents similar leverage—except the stakes involve not just information access, but the capacity to create intelligence itself. If NVIDIA maintains 75% market share through 2028, every AI breakthrough will flow through CUDA's architecture, with economic rents accruing to a single choke point. If hyperscalers successfully deploy TPUs and custom ASICs at scale, they vertically integrate the AI stack from silicon to service, potentially locking out competitors who lack billion-dollar chip design teams.

The energy dimension carries civilizational weight. Data centers already consume roughly 1% of global electricity; AI training could push that to 3–4% by 2030 if efficiency doesn't improve. TPUs' 2× performance-per-watt advantage over GPUs, compounded across millions of chips, could mean the difference between sustainable AI scaling and an energy crisis that forces rationing of compute access. Google's Ironwood, at 30× the efficiency of 2018 TPUs, exemplifies the exponential gains possible through ASIC specialization—but only if the industry moves beyond CUDA's gravitational pull.

The geopolitical contest will intensify. China's semiconductor sanctions accelerate domestic ASIC development, potentially fracturing the global AI ecosystem into incompatible hardware camps. Europe's push for "digital sovereignty" may produce regional accelerators optimized for GDPR-compliant, energy-efficient AI. The nation or bloc that achieves both high performance and energy efficiency will attract AI companies, talent, and capital, creating a virtuous cycle of innovation—while laggards face spiraling costs and competitive disadvantage.

The TPU-versus-GPU debate mirrors the historical CPU-versus-GPU transition: the answer isn't replacement, but complementary specialization. CPUs didn't disappear when GPUs accelerated graphics and then AI; they evolved into orchestrators managing heterogeneous compute. Similarly, TPUs won't eliminate GPUs, nor will GPUs' flexibility render ASICs obsolete. Instead, the future belongs to adaptive infrastructure that routes matrix multiplication to TPUs, mixed workloads to GPUs, control flow to CPUs, and I/O to specialized DPUs (data processing units).

For practitioners, the meta-lesson matters most: architectural assumptions embedded in today's models shape tomorrow's hardware, which in turn constrains future model designs. Transformers' dominance stems partly from how naturally they parallelize on GPUs; TPUs optimize for those same patterns, reinforcing the feedback loop. The next breakthrough architecture—whether state-space models, continuous-time networks, or neuromorphic computing—may favor entirely different silicon. Betting too heavily on any single hardware platform risks obsolescence when paradigms shift.

The final frontier lies in accessibility. As of 2025, spinning up 2,000–4,000 TPUs on Google Kubernetes Engine for half-hour optimization jobs remains feasible for well-funded startups like Escalante, but far beyond reach for most researchers. DataCrunch's $1.99/hour H100 instances democratize access somewhat, yet even that exceeds budgets in much of the developing world. Until AI acceleration becomes as ubiquitous and affordable as cloud storage, the benefits of both TPUs and GPUs will concentrate among a privileged few, shaping an intelligence divide that mirrors existing inequalities.

The race isn't over—it's accelerating. By the time you finish reading this, NVIDIA will have shipped another thousand H100s, Google will have processed another billion TPU-powered queries, and AMD will have closed another exaflop of the gap. The question isn't which chip wins, but which society harnesses these tools to build intelligence that serves humanity's collective flourishing rather than entrenching power in the hands of those who already possess it. That choice—between concentrated and distributed intelligence—will define the 21st century as profoundly as the choice between centralized and distributed computing defined the 20th. Choose wisely.

The accelerators you deploy today are the civilization you build tomorrow.

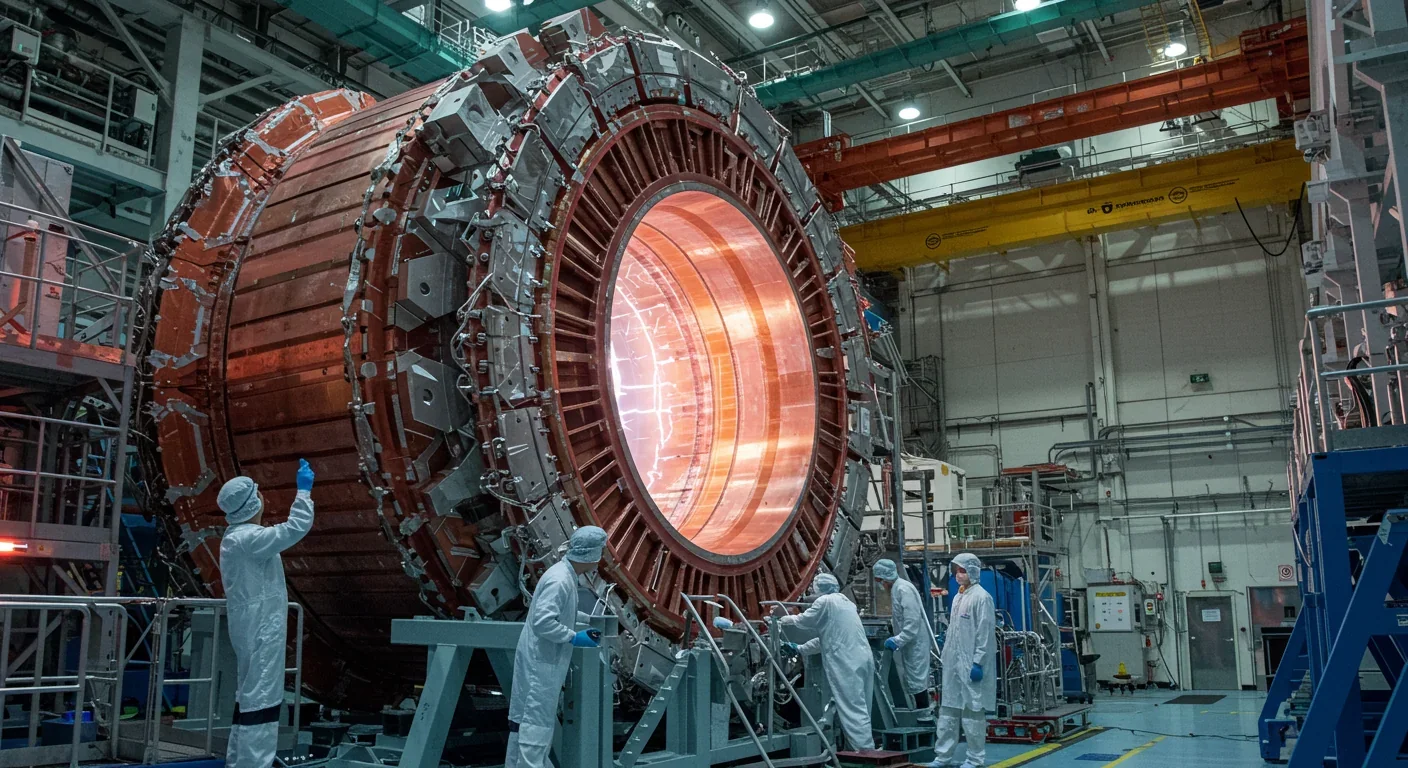

Recent breakthroughs in fusion technology—including 351,000-gauss magnetic fields, AI-driven plasma diagnostics, and net energy gain at the National Ignition Facility—are transforming fusion propulsion from science fiction to engineering frontier. Scientists now have a realistic pathway to accelerate spacecraft to 10% of light speed, enabling a 43-year journey to Alpha Centauri. While challenges remain in miniaturization, neutron management, and sustained operation, the physics barriers have ...

Epigenetic clocks measure DNA methylation patterns to calculate biological age, which predicts disease risk up to 30 years before symptoms appear. Landmark studies show that accelerated epigenetic aging forecasts cardiovascular disease, diabetes, and neurodegeneration with remarkable accuracy. Lifestyle interventions—Mediterranean diet, structured exercise, quality sleep, stress management—can measurably reverse biological aging, reducing epigenetic age by 1-2 years within months. Commercial ...

Data centers consumed 415 terawatt-hours of electricity in 2024 and will nearly double that by 2030, driven by AI's insatiable energy appetite. Despite tech giants' renewable pledges, actual emissions are up to 662% higher than reported due to accounting loopholes. A digital pollution tax—similar to Europe's carbon border tariff—could finally force the industry to invest in efficiency technologies like liquid cooling, waste heat recovery, and time-matched renewable power, transforming volunta...

Humans are hardwired to see invisible agents—gods, ghosts, conspiracies—thanks to the Hyperactive Agency Detection Device (HADD), an evolutionary survival mechanism that favored false alarms over fatal misses. This cognitive bias, rooted in brain regions like the temporoparietal junction and medial prefrontal cortex, generates religious beliefs, animistic worldviews, and conspiracy theories across all cultures. Understanding HADD doesn't eliminate belief, but it helps us recognize when our pa...

The bombardier beetle has perfected a chemical defense system that human engineers are still trying to replicate: a two-chamber micro-combustion engine that mixes hydroquinone and hydrogen peroxide to create explosive 100°C sprays at up to 500 pulses per second, aimed with 270-degree precision. This tiny insect's biochemical marvel is inspiring revolutionary technologies in aerospace propulsion, pharmaceutical delivery, and fire suppression. By 2030, beetle-inspired systems could position sat...

The U.S. faces a catastrophic care worker shortage driven by poverty-level wages, overwhelming burnout, and systemic undervaluation. With 99% of nursing homes hiring and 9.7 million openings projected by 2034, the crisis threatens patient safety, family stability, and economic productivity. Evidence-based solutions—wage reforms, streamlined training, technology integration, and policy enforcement—exist and work, but require sustained political will and cultural recognition that caregiving is ...

Every major AI model was trained on copyrighted text scraped without permission, triggering billion-dollar lawsuits and forcing a reckoning between innovation and creator rights. The future depends on finding balance between transformative AI development and fair compensation for the people whose work fuels it.